A summary truth table for the JK flip-flop. The truth table of table 2 is a summary of table 1. The last column highlights the final condition of Q n+1. The Q n+1 column comes from the S and R inputs and the truth table for the SR flip-flop. The table also displays the S and R inputs calculated for each combination of inputs. Since each grouping of J and K has two possible states of Q, the table has eight rows. Table 1 shows the four possible combinations for J and K. A2 receives the data input K and the output Q. A1 receives the data input J and the output Q̅. The JK flip-flop comprises an SR flip-flop with two added AND gates – A1 and A2. Figure 1 shows a building block of the JK flip-flop. The JK flip-flop eliminates the uncertainty in the truth table of the SR flip-flop. The letters J and K come from the initials of its inventor, Jack Kilby. The following discussion assumes positive logic – logic 1 with active high inputs. Variations to the JK flip-flop produce the master-slave D, and T flip-flops. The JK flip-flop – developed for special applications – started from it and defeated the difficulty of a forbidden input combination.

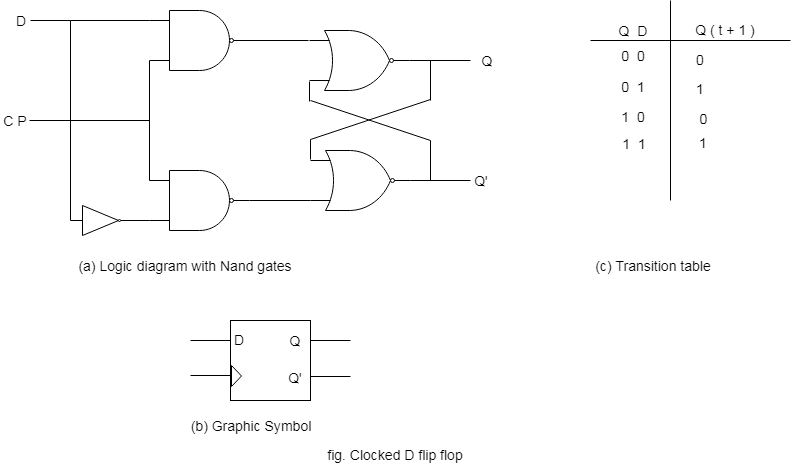

the D output changes state at half the frequency of the clock signal. What else can they be used for?īy connecting the inverting output of the D Flip Flop to the D input, a simple divide by two circuit is created i.e. For example, by cascading eight D Flip Flops in sequence, a byte (8-bits) of information can be stored after 8 clock cycles. The D Flip Flop is a building block shift registers. The D Flip Flop acts as an electronic memory component since the output remains constant unless deliberately changed by altering the state of the D input followed by a rising clock signal.

The truth table for the D Flip Flop is shown in Figure 2. A D (or Delay) Flip Flop (Figure 1) is a digital electronic circuit used to delay the change of state of its output signal (Q) until the next rising edge of a clock timing input signal occurs.

0 kommentar(er)

0 kommentar(er)